about

associations

contact

download

history

policy

canonRF

products

surplus

|

Birger was originally founded as an engineering consultancy, specializing in the

implementation of vision and compression algorithms. Birger has since evolved into a

manufacturer of products of its own design. Birger lens control systems enable the

remote and automated control of low cost consumer and professional camera lenses, and are

utilized in the machine vision, broadcast, security, surveillance and entertainment

markets. All design and manufacturing of these products is carried out by Birger, in its

Boston headquarters. Please join us for a brief tour through Birger's history.

2008: OEM Canon EF Lens Mount

|

Motion control system for Canon EF-mount lenses. Allows for remote and

automated control of Canon (and third party) EF-mount lenses. Compatible with

hundreds of lenses. Allows for accurate and repeatable, remote and automated

control of aperture and focus. Highly accurate and repeatable control. Servo

focus with 60 position updates per second. Supported by many major machine

vision camera OEMs. For more information see our "products" page.

|

|

|

2008: Canon EF Lens Mount and Remote Follow Focus for RED One Cinema Camera

Birger Engineering developed the ...

While this version for the RED One camera, is now discontinued and sold out, we

do support this level of capability with our OEM Canon EF adapter.

|

|

|

2004: Golf Ball Trajectory & Spin Rate Analysis Software

|

Typical golf ball trajectory analysis systems take double exposures of a golf

ball immediately after the time of impact, using an extremely bright strobe light

to both freeze the motion and overcome the ambient light in the scene. The

picture shown has extremely low contrast between the golf balls and the

background, due to the sunlight bleeding through the images of the balls, and the

light colored pants worn by the golfer. The top image is the original double

exposure. The bottom image represents graphically the results of the analysis.

The green color plane shows the original image with its meaningful range of

brightness expanded. The blue plane has the recovered balls plotted as perfect

circles back into the image for verification. From a single camera view, this

software application recovers both the X, Y & Z displacements and the

rotations in three axes of the second ball image relative to the first. From

this information, the geometry of the optics and the delay between the images,

all initial parameters of the golf ball flight can be readily known. The sample

image you are looking at took about 500mS to process on a 1GHz Pentium 3 laptop.

The software was written in C and has no processor specific optimizations. This

work was done for a major golf club manufacturer.

|

|

|

2003: Stereo Disparity & DeWarp FPGA Cores

|

Implementation of Woodfill's Census algorithm in Xilinx Virtex2pro FPGA operating

at 88 frames per second at 320x240 resolution (slowest speed grade). Source image

pairs at 640x480 pixels, downsampled and dewarped to 320x240. Disparity search

window 32 pixels wide, 7x7 pixel summed hamming distance windows. Design fits in

XC2VP20 with plenty of room to spare for a DDR SDRAM controller, JPEG compression

engine, nine camera frame grabber and PCI to PLB/OPB bridges. Stereo requires

2869 LUTS and 23 BRAMS and no external memory. This implementation of

dewarp used 2 PowerPCs, that would have otherwise gone unused, and 6 BRAMS. The

cores have PLB bus interfaces to talk to a common DDR SDRAM bank containing the

frame buffers. The larger FPGA was developed using the Xilinx Embedded Development

Kit (EDK 3.2). This core was used by a robot for obstacle avoidance and object tracking.

This core calculates 215 million disparities per second - which was "fast enough"

for the application. The architecture can be scaled cost effectively from one quarter to

ten times the performance. This work was done for NASA, for a robot that had been destined

to fly in the International Space Station.

|

|

|

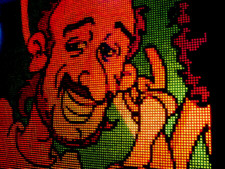

2002: 68 Billion Color LED Display

|

Birger Engineering developed the video processor and LED driver board for this display

system. The video processor has a 30bit analog video input, and a video processing engine

that provides for 36bit output. The system supports up to a resolution of 512 x 384 pixels.

The prototype display is 4M x 5M. This work was done for a customer in Brazil. The work

was also featured in the Xilinx magazine.

|

|

|

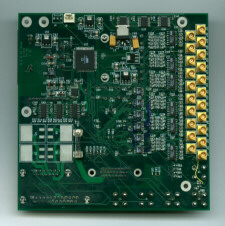

2002: PCI/MicroBlaze Compute Platform

|

Based on the Xilinx 64bit/66MHz PCI Logicore, implemented in a Virtex2-6000. Multiport SDRAM

controller, PCI to OPB bridge, PCI to SDRAM bridge, MicroBlaze, PCI64/66 master/slave 32/64bit

capable. Chipscope and uBlaze JTAG UART sharing the same JTAG port.

|

|

|

2001: Papa Camera Processing Electronics

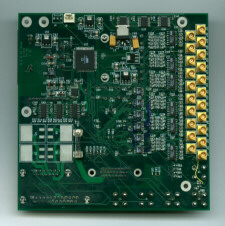

A PAPA camera uses a series of Gray coded masks oriented in both a horizontal and vertical

plane to be able to resolve the exact location any single photon enters the system, so long

as that photon does not enter the system at the exact same time as another. These cameras can

be employed with scintilation screens to image Gamma and Neutron events as well. With 21 masks

and photo-multiplier tubes, a the locations of these singular events can be located in real

time on a 2048 x 2048 grid.

The electronics are capable of processing of 21 photomultiplier tubes at a rate of up to

65MHz in a Xilinx XC2S100 FPGA. The 21 analog channels needed to have individual gain control,

as a typical batch of PMT tubes will have a gain variation of 10:1 across each of the tubes.

The gain for each of the channels is individual settable via 10 bit digital control. Any four

channels can be viewed at a 10 bit resolution simultaneously for calibration purposes. During

normal operation twenty 1 bit and three 10 bit signals are being processed to determine both

the location and the "legitimacy" af any event. The design is a single six layer PCB measuring

140mm square, with two sided component placement. The same board simultaneously generates up

to 4000V to power the photomultiplers, controls 150W thermoelectric cooler (PID and PWM in

FPGA) and measures pico-amperes across 22 analog channels.

|

|

|

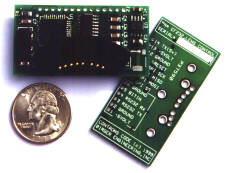

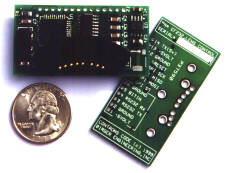

1999: The Original Birger Canon EF Lens Controller... the EF232

|

The original...

|

|

|

1999: High Speed Template Matching - UPGRADE

|

Customer had existing three VME-card set employing six FPGAs used as the image processor in a

Re-implemented Customer FPGA design to increase performance of template matching algorithm by

a factor of four without requiring changes to the physical hardware, or speed grade of FPGA employed.

|

|

|

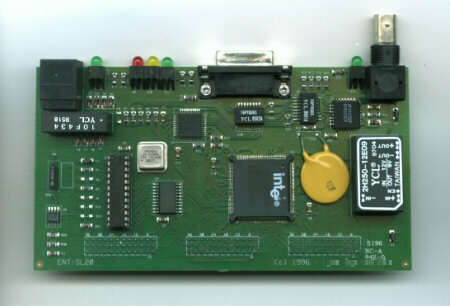

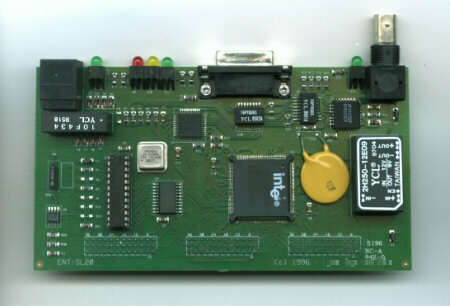

1996: Ethernet Interface

|

Plug in card for a linescan camera used for photo timing sporting events. Incorporates

Intel i960 Bus Interface. Autoselects 10baseT, 10base2, and AUI. This is the first project

completed after our founding in 1996. At the time we were known as "23rd Hour Engineering".

|

|

|

|

|

|